M-R 內部模擬出五核心的CPU架構,如下圖:

每一核心各自有

- 一個運算單元 ACC

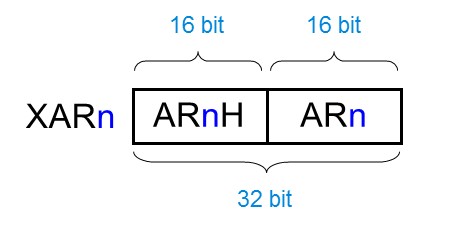

- 六個輔助暫存器(XAR0~XAR5)

DATA區 (DV, DH, MV, MH…)還有Code (程式區)是五核共用的。

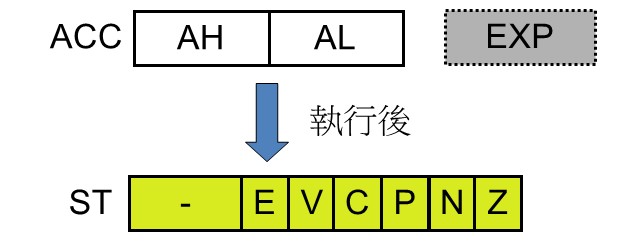

ACC 暫存器包含 AH(高位 16bits)、AL(低位 16bits)、EXP (指數 16bits,浮點數時才用到)

ACC 主要用來做數學/邏輯運算,另外操作參數與系統變數,可根據指令的型態來儲存整數(16 / 32 bit) 與浮點數(48 bit) ,且可與不同資料型態(整數或浮點數)的資料做四則運算無須轉型,運算或寫出操作過程ACC 始終保持最高精度。

XARn 暫存器包含 ARnH (高位 16bits)、ARn(低位 16bits), n=0~5(共六組)

輔助暫存器 XARn 最常用在ACC運算過程中儲存暫時的數值,而無須用到外部的 Data 區(DV, DH…),另外還用間接定址 *ARn還有迴圈,但是要記得XARn 只能儲存整數(16/32 bits),若運算過程需暫存浮點數則還是需要借用 Data區(DV, DH, MV, MH…)

另外ST 暫存器會在指令執行後根據 ACC 結果修改相關的狀態旗標

其中比較常用到的狀態有

- Z:零旗標,當 ACC 內容為零或ACC與其他數值比較相同時會輸出。

- N:負旗標,當 ACC 內容為負數或ACC與其他數值比較較小會輸出。

- P:正旗標,當 ACC 內容為正數或ACC與其他數值比較較大會輸出。

- E:錯誤旗標,當指令執行結果有錯誤,其錯誤碼可參考 ERR 暫存器號碼解讀,此時驅動器會跳AL.F21(指令執行錯誤的警告)

ST暫存器主要是拿來做控制程式流程,例如 JMP_C 指令,可執行條件跳躍!